# SAY NO TO AN UNRULY POWER DELIVERY SYSTEM

Dr. Mandy Pant Intel Corporation

#### **MANDY PANT**

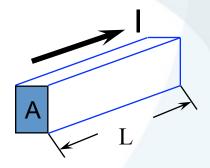

### **Background: Resistance (R)**

- Material's <u>opposition to flow of charge</u> (current)

- Units: Ohms (Ω)

- Key parameters that affect R

- Resistivity

- Cross-sectional area (thickness, width)

- Length

- Measurement: Simple

- Impacts DC voltage drop as V=IR

$$R = \rho L / A$$

$\rho$  = Material Resistivity ( $\Omega$ -cm)

#### **Background: Inductance (L)**

- Material's opposition to change in flow of charge

- Units: Henry (H)

- Discovered by M. Faraday in 1831

- Key parameters that affect L

- Fairly complex parameter

- Dependent on overall current path

- Measurement: Difficult (dynamically dependent)

- Requires special test fixtures and calibration methods

- Impacts AC voltage drop as V = L\*di/dt

- Self Inductance: Inductance of a conductor

- Proportional to length

- Depends weakly on geometry cross section

- Mutual Inductance: Coupled inductance between two conductors

- Affected by separation and material between conductors

- Loop inductance: Inductance of a closed loop conductor

- Usually biggest perpetrator

- Proportional to loop area

- Bringing Power/Ground rails closer to signal lines drops loop inductance but increases mutual inductance

- High inductance is <u>NOT</u> good for IC Power Delivery system

- Reduces circuit switching speed (timing impact)

- Create undershoot and overshoot

- Increase supply voltage fluctuation

$L = \phi N/I$   $\phi = Magnetic flux (H-Amp$

### **Background: Capacitance (C)**

- Material's ability to <u>store charge</u>

- Units: Farad (F)

- Discovered by van Mussenbroek in 1745

- Measurement: Impedance Analyzer or Network Analyzer

- Requires special test fixtures and/or calibration methods

- Act as a charge reservoir (battery) to provide charge to power grid and local circuit elements

- Distributed along entire power delivery system (from on-die to VRM)

$C = \varepsilon A/d \ (\mu F, nF, pF)$  $\varepsilon = dielectric constant$

#### **Background**

- Ohm's Law

- $\vee$  = |Z|

- Where V = voltage, I is current and Z is impedance

- -V = I\*R + L\*di/dt

- where

I = C\*dV/dt

V = Voltage

I = Current

t = Time

R= resistance

L = inductance

C = capacitance

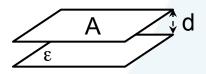

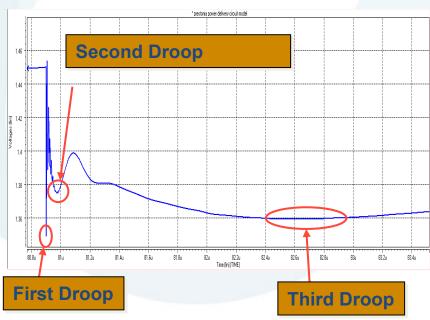

#### **Power supply droops**

#### First, Second and Third Droops

Increasing lower frequency and amplitude but longer duration of voltage dips seen in power supply

Typical voltage response of power delivery system

### A "well-behaved" power grid

Goal: Deliver predictable and desired voltage

To all transistors

Under all operating conditions

Over lifetime of chip

Desired characteristics

Low impedance

Low IR drop (DC)

Low L\*di/dt droop (AC)

Robust EM reliability

Metal/contact wear-out minimized

over part's lifetime

Power delivery system impacts all aspects of design

Functionality, performance, reliability & power consumption

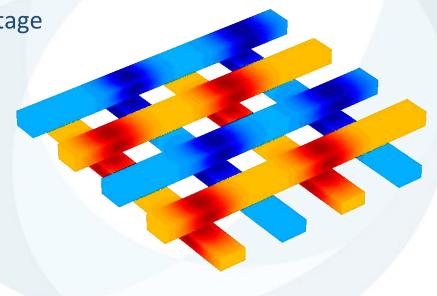

## **Modern Day On-Die Power Grid**

- C4 bump connections

- V<sub>DD</sub> and GND pins all over chip surface

- Power enters from top metal layer via bumps

- Grid brings in power across various metal layers onto the die

- Most current for devices drawn from "nearby" connections

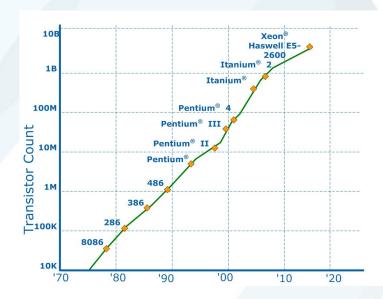

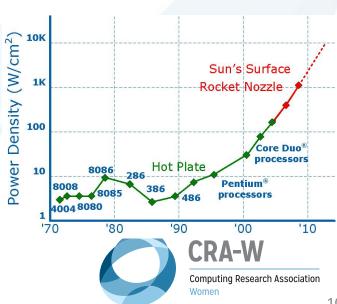

#### **Technology Trends: Moore's Law**

- More and faster transistors with higher power demands

- Gate delay ◆30% every process generation (2 years)

- Leakage currents

- Impact: Hurts IR, AC drops, EM

- Area of a transistor roughly scales by 50% per generation

- Transistor density doubling

- Power density increasing

- Design complexity increasing

- ■I<sub>MAX</sub> requirements

- Impact: Hurts peak IR drop, EM

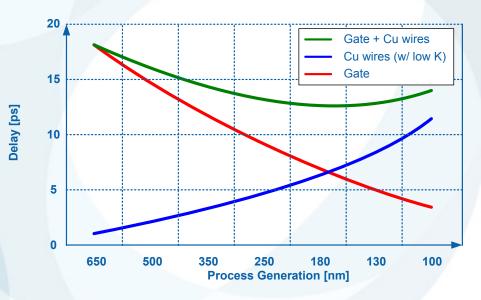

- Delay Trends

- Cross-chip communication

- Takes multiple cycles to cross a chip

- Impact: Longer relative time taken by charge to flow from capacitors to switching transistors

Wire & gate delay trends

- 8-14+ metal layers in modern processes

- More degrees of freedom for trade-off between interconnect and power grid → More effort in grid design

- <u>Impact:</u> Increased impedance between VR and device

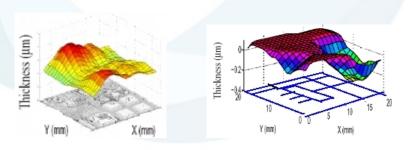

- Thinner wires and smaller vias/contacts

- Increased effects of

- Electron surface scattering

- Finite barrier thickness

- <u>Impact:</u> Higher resistance; hurts IR drop

- More design restrictions on wires

- Cu and advanced CMP processes place more design restrictions

- Example: maximum width, metal density, oxide density within metal area etc

- Impact: Less knobs to play with when designing power grid

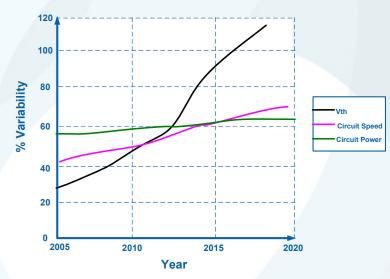

- In-die process variations

- V<sub>th</sub> variation

- Variation in parasitics

- Variations in die ageing

- Impact: Alters power grid impedance, current demand, hurts reliability

- » Different parts of the die run at different speeds and temp

**Data extracted from ITRS 2005**

Cu Thickness Variation

- C4 bump pitch has not been scaling as fast as transistor technology while current density is scaling

- Impact: Increasing current per bump which will stretch reliability limits

- Hot spots with higher current density reduce bump Imax (temp dependent)

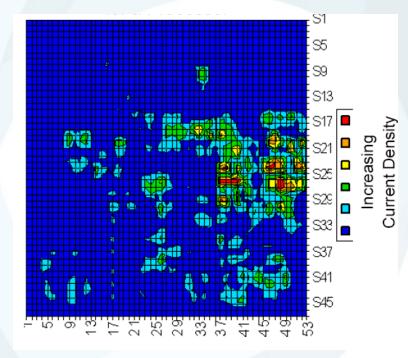

C4 Bump Current Density for Sample Micro processor

#### **Power Grid Challenges: Design**

- Multiple voltage domains on-die

- Trick used to reduce power while maintaining performance

- Cache voltage lower than core/uncore voltage

- Cache mainly needs to hold state

- Speed critical for execution units, overall communication etc → leads to higher voltage requirements here

- Impact

- Overall grid metal available per domain reduced

- May need to compromise grid requirements depending upon distribution of voltage domains

- Voltage islands may impact power delivery

- Dynamically switching on/off gated-voltage domains without hurting the power grid is a challenge

#### **Power Grid Challenges: Tools**

- Require robust CAD tools for

- Power grid design

- Determine optimal % of metal used for power allocation in each metal layer

- Distribution

- Based on EM rules, sample current signatures, routing constraints, power supply noise margins

- Require robust CAD tools for

- Analysis

- Evaluate behavior of grids in layout as we move along design cycle

- Verification

- Validate the built grid can meet constant/instantaneous current needs throughout life time of part

- Require standardized tools for IR/AC droop prediction and EM verification

- Inherent uncertainty in tools

- Computationally intensive analysis

- Most issues found after the manufactured chip comes back

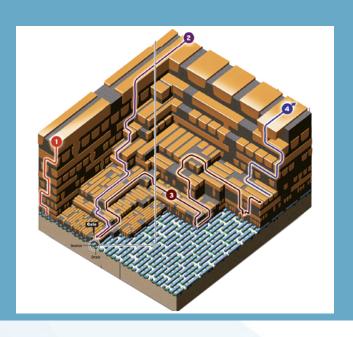

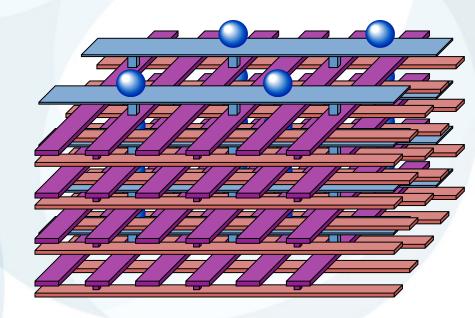

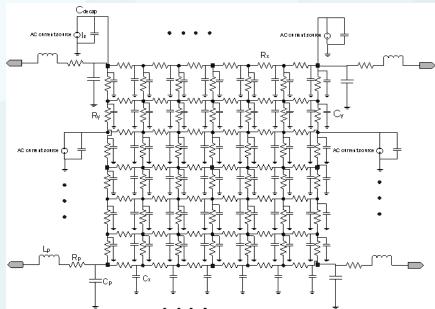

#### **Sample Global Power Distribution Network**

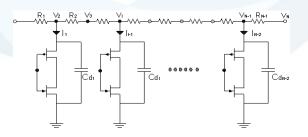

#### **Sample Local Power Supply Network**

#### **Power Delivery System**

- Need to tackle technology trends, design and tool challenges to avoid "unruly" power grid behavior (complexity of data/tool)

- Requires us to use clever tricks to deal with technology

- Requires us to use clever tricks in design

- Regularity of grid, decoupling caps, uniform current loading etc

- Requires us to use clever tools that can calculate and project actual behavior of the power delivery system during microprocessor design cycles

- Can we develop easy methods to design and accurately + rapidly analyze the increasingly complex power grid and its role in the overall power delivery system?

- Today's set is just a tip of the iceberg

- Lots of research opportunities

# MENTORING SESSION: BUILDING YOUR SELF-CONFIDENCE

Dr. Mandy Pant Intel Corporation

#### **Self Confidence**

- A feeling of trust in one's abilities, qualities, and judgment

- Too little can lead to not taking on enough risk, a lack of success, decreased self confidence

- Too much can lead to taking on too much risk, frequent failure to deliver, letting down colleagues/ collaborators

- Two primary contributors

- Self efficacy

- Belief in your capacity to produce an achievement

- To exert control over your motivation, behavior, and social env

- Self esteem

- Your overall evaluation of yourself and your right to be happy

#### How Self-confident are you?

# High Self-confidence

- Do what you believe to be right, even if criticized for it

- Willing to take risks

- Admit your mistakes and learn from them

- Extol your virtues often

- Accept compliments graciously: "Thanks, I really worked hard on that paper."

## Low Self-confidence

- Govern your behavior based on what others think

- Stay in your comfort zone

- Work hard to cover up your mistakes

- Wait for others to congratulate you

- Dismiss compliments: "Oh that paper was nothing really, anyone could have done it."

#### 20+ Actions to Boost your Self-confidence

- Think and act positive

- Kill negative thoughts

- Groom yourself

- Get prepared

- Be generous and kind

- Know your principles and live by them

- Stand tall

- Speak slowly

- Increase competence

- Set a small goal and achieve it

- Recognize when there is a problem; find support

- Change a small habit

- Focus on solutions

- Volunteer

- Exercise

- Be active

- Do something you have been procrastinating over

- Work on small things

- Clear your desk

- Don't let men allow you to think that they are better than you

- Don't ever ever put yourself down AND

- Smile ☺

#### **Beware of the Imposter Syndrome**

**Regardless** of success achieved or proof of competence, you are sometimes convinced that you do not deserve it

- Proof is dismissed as luck, timing, or a result of deceiving others into thinking you are more intelligent/competent than you are

- It is particularly common among successful women and typically associated with academics. It is also widely found among graduate students and first generation college students.

#### Believe in yourself

No one will believe in you unless you believe in yourself

"Somehow I can't believe that there are any heights that can't be scaled by a [person] who knows the secret of making dreams come true. This special secret, it seems to me, can be summarized in the four C's. They are Curiosity, Confidence, Courage, and Constancy, and the greatest of all is Confidence. When you believe in a thing, believe in it all the way, implicitly and without question." - Walt Disney